Vol. 3B 22-21

ARCHITECTURE COMPATIBILITY

22.25.1 Machine-Check

Architecture

The Pentium Pro processor introduced a new architecture to the IA-32 for handling and reporting on machine-

check exceptions. This machine-check architecture (described in detail in Chapter 15, “Machine-

Check Architecture”) greatly expands the ability of the processor to report on internal hardware errors.

22.25.2 Priority of Exceptions

The priority of exceptions are broken down into several major categories:

1. Traps on the previous instruction

2. External interrupts

3. Faults on fetching the next instruction

4. Faults in decoding the next instruction

5. Faults on executing an instruction

There are no changes in the priority of these major categories between the different processors, however, excep-

tions within these categories are implementation dependent and may change from processor to processor.

22.25.3 Exception Conditions of Legacy SIMD Instructions Operating on MMX Registers

MMX instructions and a subset of SSE, SSE2, SSSE3 instructions operate on MMX registers. The exception condi-

tions of these instructions are described in the following tables.

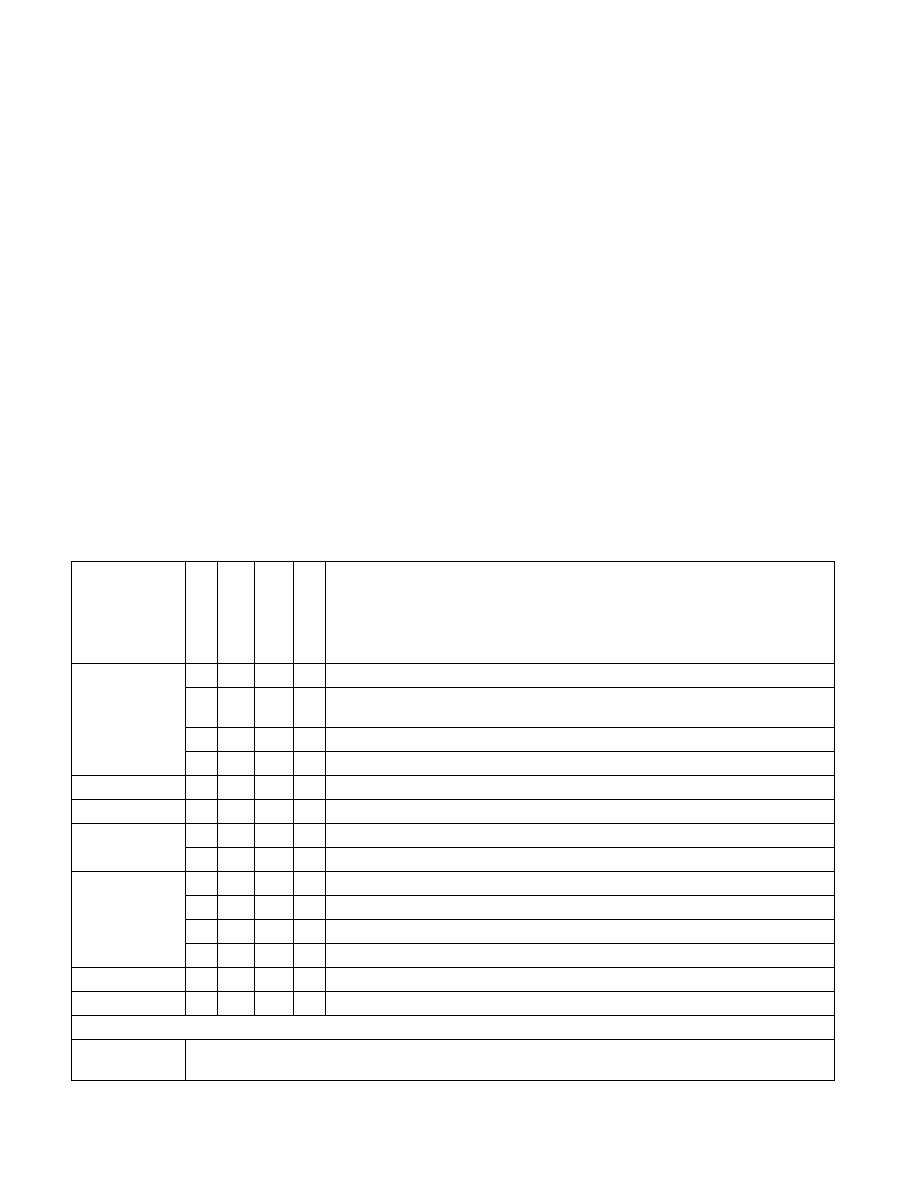

Table 22-4. Exception Conditions for Legacy SIMD/MMX Instructions with FP Exception and 16-Byte Alignment

Exception

Re

al

Vi

rtual-8086

Pr

ot

ec

ted and

Co

mp

at

ib

ilit

y

64-bi

t

Cause of Exception

Invalid Opcode,

#UD

X

X

X

X

If an unmasked SIMD floating-point exception and CR4.OSXMMEXCPT[bit 10] = 0.

X

X

X

X

If CR0.EM[bit 2] = 1.

If CR4.OSFXSR[bit 9] = 0.

X

X

X

X

If preceded by a LOCK prefix (F0H)

X

X

X

X

If any corresponding CPUID feature flag is ‘0’

#MF

X

X

X

X

If there is a pending X87 FPU exception

#NM

X

X

X

X

If CR0.TS[bit 3]=1

Stack, SS(0)

X

For an illegal address in the SS segment

X

If a memory address referencing the SS segment is in a non-canonical form

General Protec-

tion, #GP(0)

X

X

X

X

Legacy SSE: Memory operand is not 16-byte aligned

X

For an illegal memory operand effective address in the CS, DS, ES, FS or GS segments.

X

If the memory address is in a non-canonical form.

X

X

If any part of the operand lies outside the effective address space from 0 to FFFFH

#PF(fault-code)

X

X

X

For a page fault

#XM

X

X

X

X

If an unmasked SIMD floating-point exception and CR4.OSXMMEXCPT[bit 10] = 1

Applicable

Instructions

CVTPD2PI, CVTTPD2PI