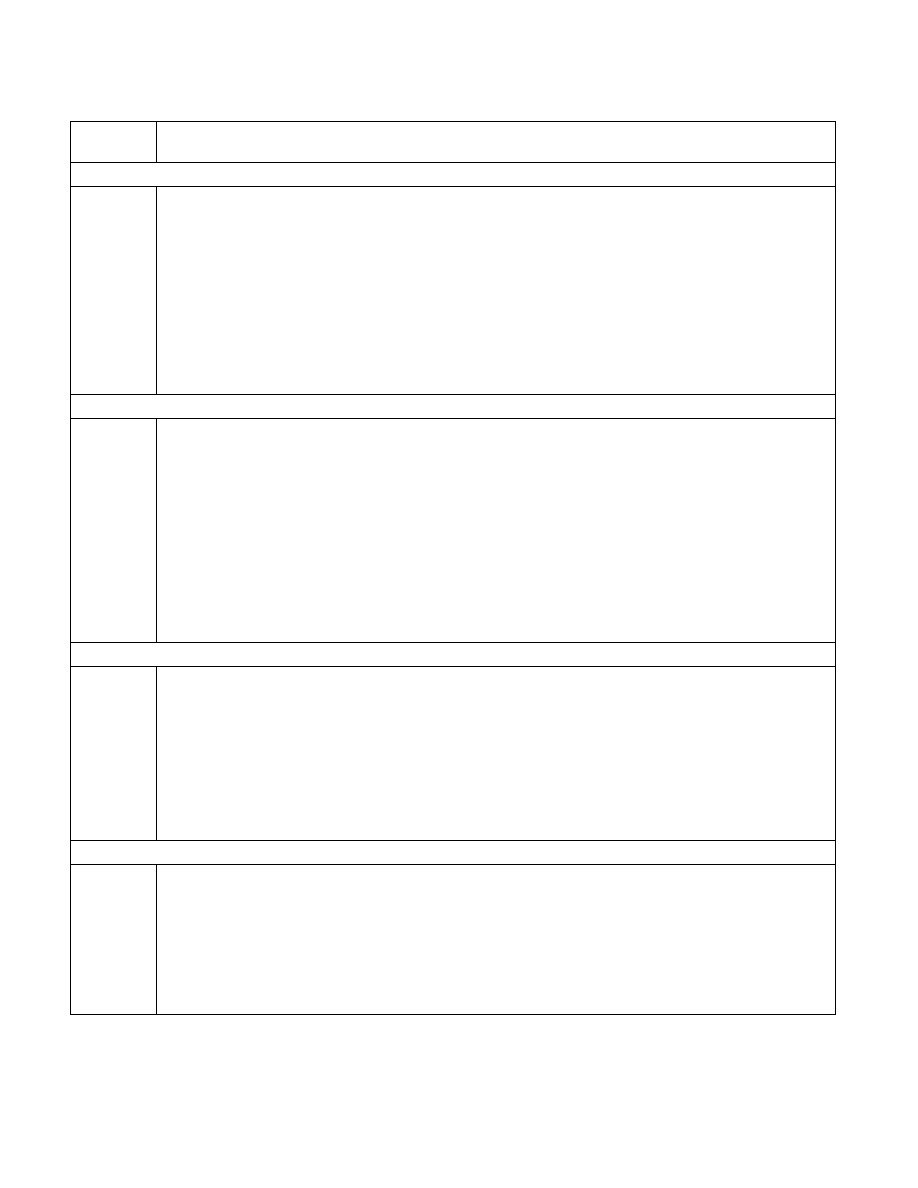

CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

Vol. 2A 3-197

Intel Resource Director Technology (Intel RDT) Allocation Enumeration Sub-leaf (EAX = 10H, ECX = 0)

10H

NOTES:

Leaf 10H output depends on the initial value in ECX.

Sub-leaf index 0 reports valid resource identification (ResID) starting at bit position 1 of EBX.

EAX

Reserved.

EBX

Bit 00: Reserved.

Bit 01: Supports L3 Cache Allocation Technology if 1.

Bit 02: Supports L2 Cache Allocation Technology if 1.

Bits 31 - 03: Reserved.

ECX

Reserved.

EDX

Reserved.

L3 Cache Allocation Technology Enumeration Sub-leaf (EAX = 10H, ECX = ResID =1)

10H

NOTES:

Leaf 10H output depends on the initial value in ECX.

EAX

Bits 4 - 00: Length of the capacity bit mask for the corresponding ResID using minus-one notation.

Bits 31 - 05: Reserved.

EBX

Bits 31 - 00: Bit-granular map of isolation/contention of allocation units.

ECX

Bit 00: Reserved.

Bit 01: Updates of COS should be infrequent if 1.

Bit 02: Code and Data Prioritization Technology supported if 1.

Bits 31 - 03: Reserved.

EDX

Bits 15 - 00: Highest COS number supported for this ResID.

Bits 31 - 16: Reserved.

L2 Cache Allocation Technology Enumeration Sub-leaf (EAX = 10H, ECX = ResID =2)

10H

NOTES:

Leaf 10H output depends on the initial value in ECX.

EAX

Bits 4 - 00: Length of the capacity bit mask for the corresponding ResID using minus-one notation.

Bits 31 - 05: Reserved.

EBX

Bits 31 - 00: Bit-granular map of isolation/contention of allocation units.

ECX

Bits 31 - 00: Reserved.

EDX

Bits 15 - 00: Highest COS number supported for this ResID.

Bits 31 - 16: Reserved.

Intel SGX Capability Enumeration Leaf, sub-leaf 0 (EAX = 12H, ECX = 0)

12H

NOTES:

Leaf 12H sub-leaf 0 (ECX = 0) is supported if CPUID.(EAX=07H, ECX=0H):EBX[SGX] = 1.

EAX

Bit 00: SGX1. If 1, Indicates Intel SGX supports the collection of SGX1 leaf functions.

Bit 01: SGX2. If 1, Indicates Intel SGX supports the collection of SGX2 leaf functions.

Bit 31 - 02: Reserved.

EBX

Bit 31 - 00: MISCSELECT. Bit vector of supported extended SGX features.

ECX

Bit 31 - 00: Reserved.

Table 3-8. Information Returned by CPUID Instruction (Contd.)

Initial EAX

Value

Information Provided about the Processor