CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

3-196 Vol. 2A

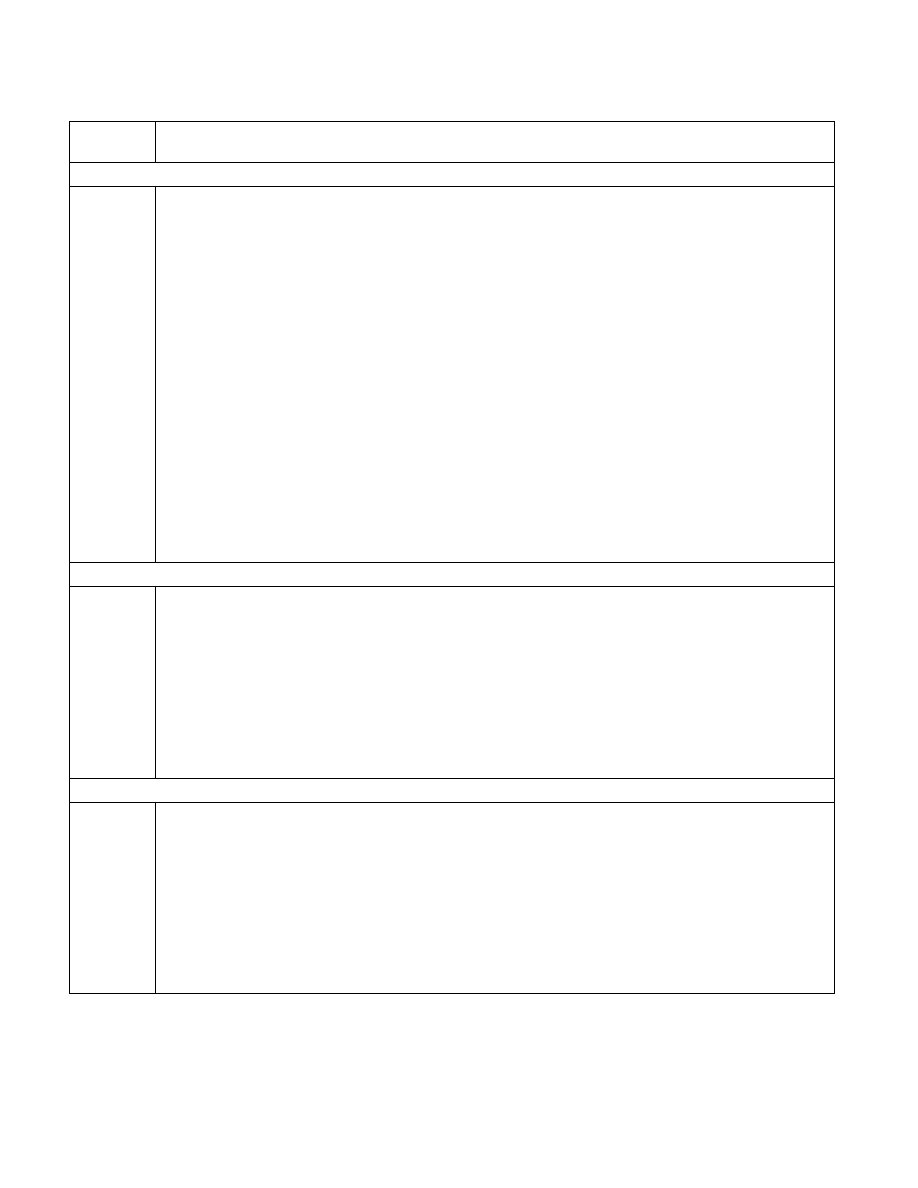

Processor Extended State Enumeration Sub-leaves (EAX = 0DH, ECX = n, n > 1)

0DH

NOTES:

Leaf 0DH output depends on the initial value in ECX.

Each sub-leaf index (starting at position 2) is supported if it corresponds to a supported bit in either the

XCR0 register or the IA32_XSS MSR.

* If ECX contains an invalid sub-leaf index, EAX/EBX/ECX/EDX return 0. Sub-leaf n (0 ≤ n ≤ 31) is invalid

if sub-leaf 0 returns 0 in EAX[n] and sub-leaf 1 returns 0 in ECX[n]. Sub-leaf n (32 ≤ n ≤ 63) is invalid if

sub-leaf 0 returns 0 in EDX[n-32] and sub-leaf 1 returns 0 in EDX[n-32].

EAX

Bits 31 - 0: The size in bytes (from the offset specified in EBX) of the save area for an extended state

feature associated with a valid sub-leaf index, n.

EBX

Bits 31 - 0: The offset in bytes of this extended state component’s save area from the beginning of the

XSAVE/XRSTOR area.

This field reports 0 if the sub-leaf index, n, does not map to a valid bit in the XCR0 register*.

ECX

Bit 00 is set if the bit n (corresponding to the sub-leaf index) is supported in the IA32_XSS MSR; it is clear

if bit n is instead supported in XCR0.

Bit 01 is set if, when the compacted format of an XSAVE area is used, this extended state component

located on the next 64-byte boundary following the preceding state component (otherwise, it is located

immediately following the preceding state component).

Bits 31 - 02 are reserved.

This field reports 0 if the sub-leaf index, n, is invalid*.

EDX

This field reports 0 if the sub-leaf index, n, is invalid*; otherwise it is reserved.

Intel Resource Director Technology (Intel RDT) Monitoring Enumeration Sub-leaf (EAX = 0FH, ECX = 0)

0FH

NOTES:

Leaf 0FH output depends on the initial value in ECX.

Sub-leaf index 0 reports valid resource type starting at bit position 1 of EDX.

EAX

Reserved.

EBX

Bits 31 - 00: Maximum range (zero-based) of RMID within this physical processor of all types.

ECX

Reserved.

EDX

Bit 00: Reserved.

Bit 01: Supports L3 Cache Intel RDT Monitoring if 1.

Bits 31 - 02: Reserved.

L3 Cache Intel RDT Monitoring Capability Enumeration Sub-leaf (EAX = 0FH, ECX = 1)

0FH

NOTES:

Leaf 0FH output depends on the initial value in ECX.

EAX

Reserved.

EBX

Bits 31 - 00: Conversion factor from reported IA32_QM_CTR value to occupancy metric (bytes).

ECX

Maximum range (zero-based) of RMID of this resource type.

EDX

Bit 00: Supports L3 occupancy monitoring if 1.

Bit 01: Supports L3 Total Bandwidth monitoring if 1.

Bit 02: Supports L3 Local Bandwidth monitoring if 1.

Bits 31 - 03: Reserved.

Table 3-8. Information Returned by CPUID Instruction (Contd.)

Initial EAX

Value

Information Provided about the Processor