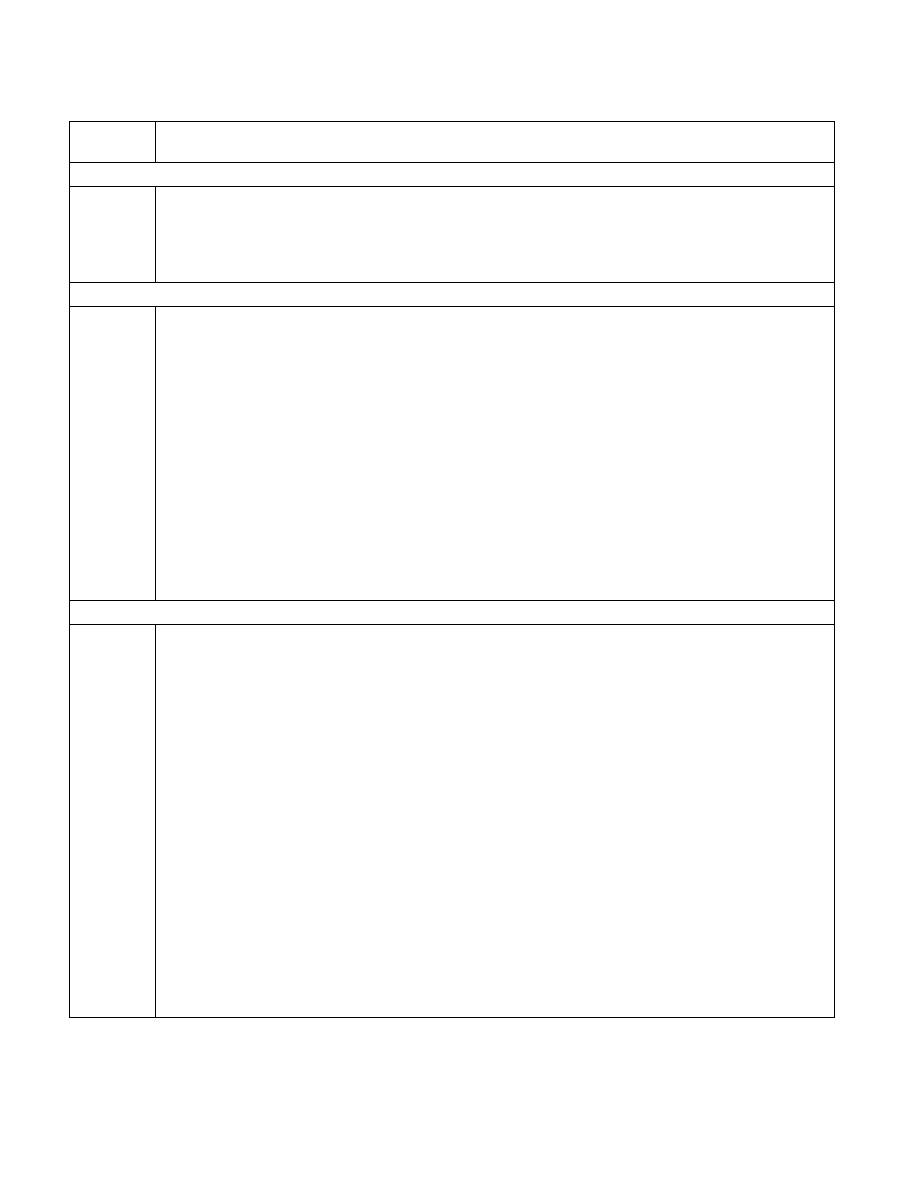

CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

3-194 Vol. 2A

Direct Cache Access Information Leaf

09H

EAX

Value of bits [31:0] of IA32_PLATFORM_DCA_CAP MSR (address 1F8H).

EBX

Reserved.

ECX

Reserved.

EDX

Reserved.

Architectural Performance Monitoring Leaf

0AH

EAX

Bits 07 - 00: Version ID of architectural performance monitoring.

Bits 15 - 08: Number of general-purpose performance monitoring counter per logical processor.

Bits 23 - 16: Bit width of general-purpose, performance monitoring counter.

Bits 31 - 24: Length of EBX bit vector to enumerate architectural performance monitoring events.

EBX

Bit 00: Core cycle event not available if 1.

Bit 01: Instruction retired event not available if 1.

Bit 02: Reference cycles event not available if 1.

Bit 03: Last-level cache reference event not available if 1.

Bit 04: Last-level cache misses event not available if 1.

Bit 05: Branch instruction retired event not available if 1.

Bit 06: Branch mispredict retired event not available if 1.

Bits 31 - 07: Reserved = 0.

ECX

Reserved = 0.

EDX

Bits 04 - 00: Number of fixed-function performance counters (if Version ID > 1).

Bits 12 - 05: Bit width of fixed-function performance counters (if Version ID > 1).

Reserved = 0.

Extended Topology Enumeration Leaf

0BH

NOTES:

Most of Leaf 0BH output depends on the initial value in ECX.

The EDX output of leaf 0BH is always valid and does not vary with input value in ECX.

Output value in ECX[7:0] always equals input value in ECX[7:0].

For sub-leaves that return an invalid level-type of 0 in ECX[15:8]; EAX and EBX will return 0.

If an input value n in ECX returns the invalid level-type of 0 in ECX[15:8], other input values with ECX >

n also return 0 in ECX[15:8].

EAX

Bits 04 - 00: Number of bits to shift right on x2APIC ID to get a unique topology ID of the next level type*.

All logical processors with the same next level ID share current level.

Bits 31 - 05: Reserved.

EBX

Bits 15 - 00: Number of logical processors at this level type. The number reflects configuration as shipped

by Intel**.

Bits 31- 16: Reserved.

ECX

Bits 07 - 00: Level number. Same value in ECX input.

Bits 15 - 08: Level type***.

Bits 31 - 16: Reserved.

EDX

Bits 31- 00: x2APIC ID the current logical processor.

NOTES:

* Software should use this field (EAX[4:0]) to enumerate processor topology of the system.

Table 3-8. Information Returned by CPUID Instruction (Contd.)

Initial EAX

Value

Information Provided about the Processor