CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

Vol. 2A 3-193

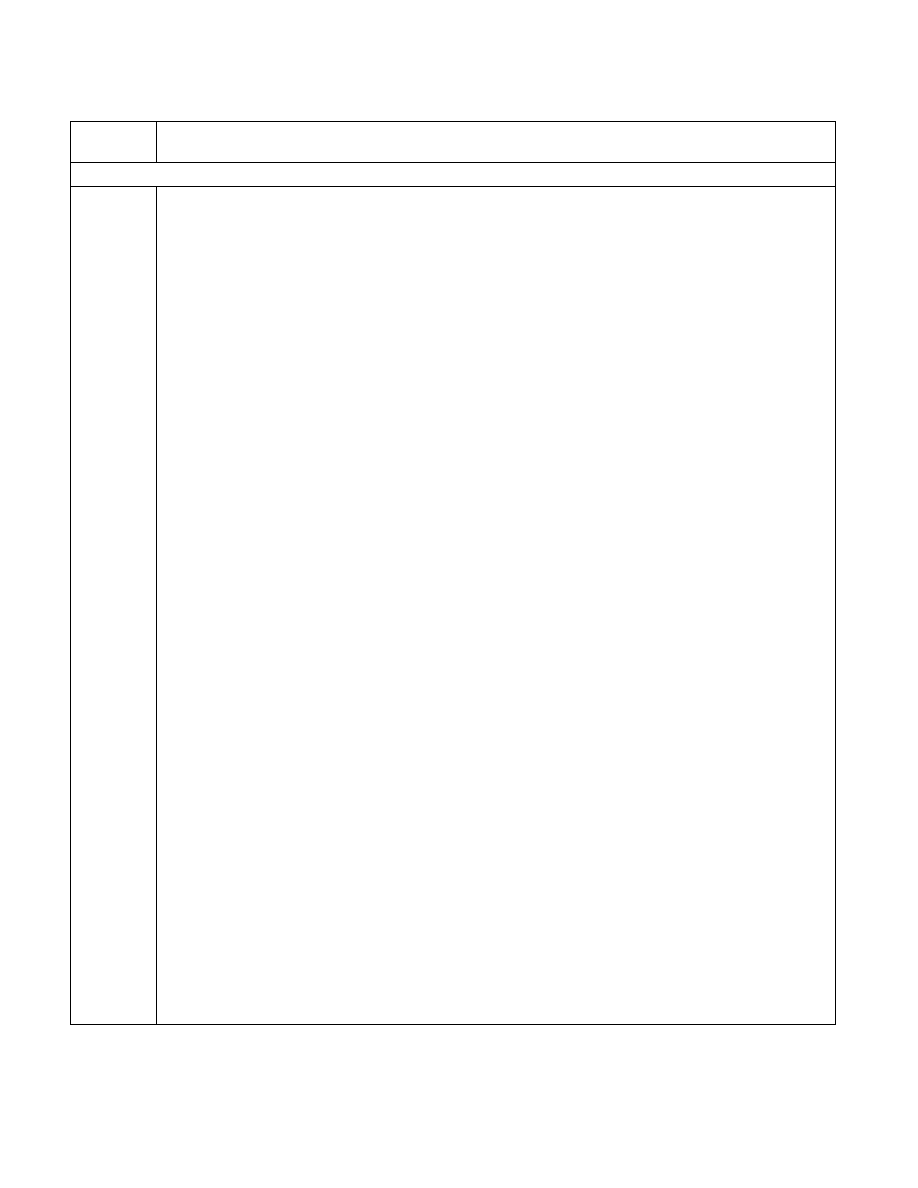

Structured Extended Feature Flags Enumeration Leaf (Output depends on ECX input value)

07H

Sub-leaf 0 (Input ECX = 0). *

EAX

Bits 31 - 00: Reports the maximum input value for supported leaf 7 sub-leaves.

EBX

Bit 00: FSGSBASE. Supports RDFSBASE/RDGSBASE/WRFSBASE/WRGSBASE if 1.

Bit 01: IA32_TSC_ADJUST MSR is supported if 1.

Bit 02: SGX. Supports Intel® Software Guard Extensions (Intel® SGX Extensions) if 1.

Bit 03: BMI1.

Bit 04: HLE.

Bit 05: AVX2.

Bit 06: FDP_EXCPTN_ONLY. x87 FPU Data Pointer updated only on x87 exceptions if 1.

Bit 07: SMEP. Supports Supervisor-Mode Execution Prevention if 1.

Bit 08: BMI2.

Bit 09: Supports Enhanced REP MOVSB/STOSB if 1.

Bit 10: INVPCID. If 1, supports INVPCID instruction for system software that manages process-context

identifiers.

Bit 11: RTM.

Bit 12: RDT-M. Supports Intel® Resource Director Technology (Intel® RDT) Monitoring capability if 1.

Bit 13: Deprecates FPU CS and FPU DS values if 1.

Bit 14: MPX. Supports Intel® Memory Protection Extensions if 1.

Bit 15: RDT-A. Supports Intel® Resource Director Technology (Intel® RDT) Allocation capability if 1.

Bits 17:16: Reserved.

Bit 18: RDSEED.

Bit 19: ADX.

Bit 20: SMAP. Supports Supervisor-Mode Access Prevention (and the CLAC/STAC instructions) if 1.

Bits 22 - 21: Reserved.

Bit 23: CLFLUSHOPT.

Bit 24: Reserved.

Bit 25: Intel Processor Trace.

Bits 28 - 26: Reserved.

Bit 29: SHA. supports Intel® Secure Hash Algorithm Extensions (Intel® SHA Extensions) if 1.

Bits 31 - 30: Reserved.

ECX

Bit 00: PREFETCHWT1.

Bit 01: Reserved.

Bit 02: UMIP. Supports user-mode instruction prevention if 1.

Bit 03: PKU. Supports protection keys for user-mode pages if 1.

Bit 04: OSPKE. If 1, OS has set CR4.PKE to enable protection keys (and the RDPKRU/WRPKRU instruc-

tions).

Bits 16 - 5: Reserved.

Bits 21 - 17: The value of MAWAU used by the BNDLDX and BNDSTX instructions in 64-bit mode.

Bit 22: RDPID. Supports Read Processor ID if 1.

Bits 29 - 23: Reserved.

Bit 30: SGX_LC. Supports SGX Launch Configuration if 1.

Bit 31: Reserved.

EDX

Reserved.

NOTE:

* If ECX contains an invalid sub-leaf index, EAX/EBX/ECX/EDX return 0. Sub-leaf index n is invalid if n

exceeds the value that sub-leaf 0 returns in EAX.

Table 3-8. Information Returned by CPUID Instruction (Contd.)

Initial EAX

Value

Information Provided about the Processor