CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

3-192 Vol. 2A

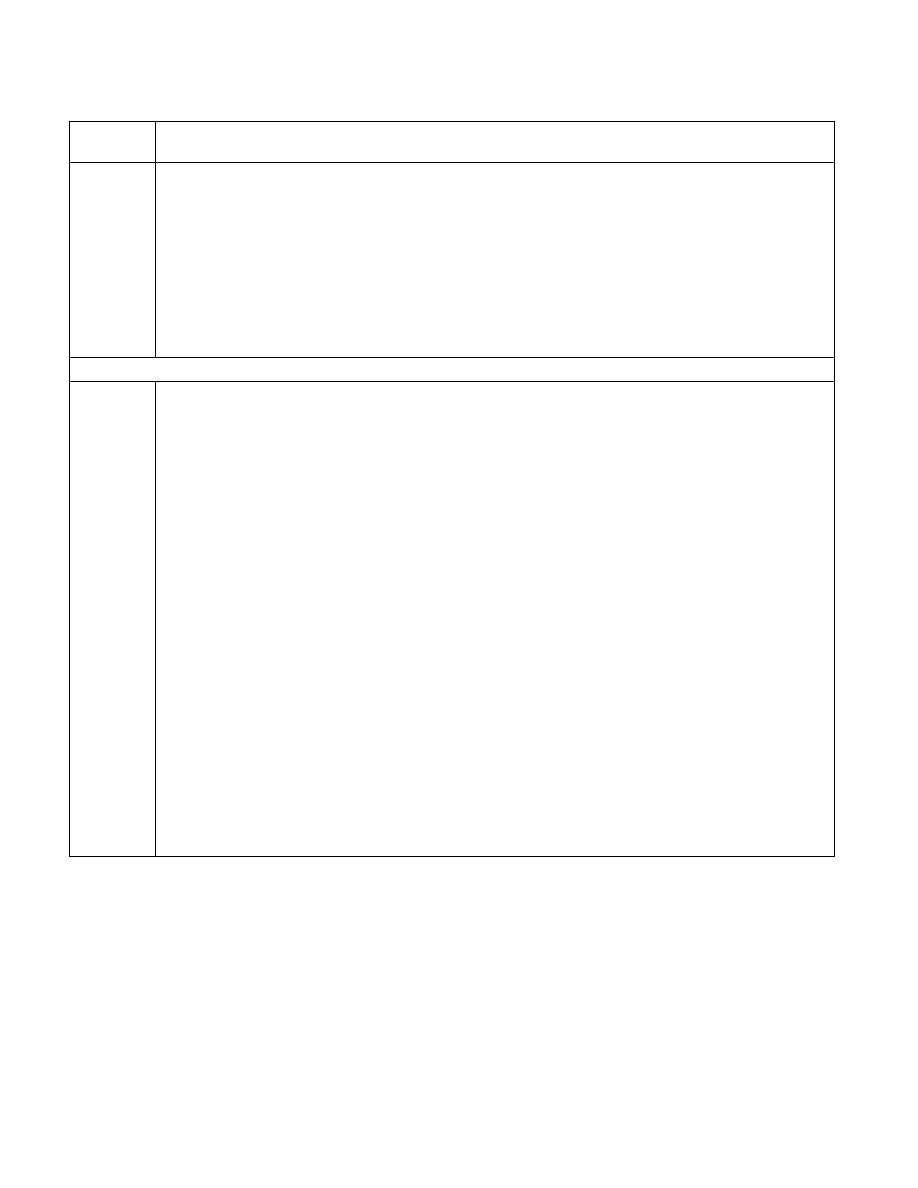

EDX

Bits 03 - 00: Number of C0* sub C-states supported using MWAIT.

Bits 07 - 04: Number of C1* sub C-states supported using MWAIT.

Bits 11 - 08: Number of C2* sub C-states supported using MWAIT.

Bits 15 - 12: Number of C3* sub C-states supported using MWAIT.

Bits 19 - 16: Number of C4* sub C-states supported using MWAIT.

Bits 23 - 20: Number of C5* sub C-states supported using MWAIT.

Bits 27 - 24: Number of C6* sub C-states supported using MWAIT.

Bits 31 - 28: Number of C7* sub C-states supported using MWAIT.

NOTE:

* The definition of C0 through C7 states for MWAIT extension are processor-specific C-states, not ACPI C-

states.

Thermal and Power Management Leaf

06H

EAX

Bit 00: Digital temperature sensor is supported if set.

Bit 01: Intel Turbo Boost Technology Available (see description of IA32_MISC_ENABLE[38]).

Bit 02: ARAT. APIC-Timer-always-running feature is supported if set.

Bit 03: Reserved.

Bit 04: PLN. Power limit notification controls are supported if set.

Bit 05: ECMD. Clock modulation duty cycle extension is supported if set.

Bit 06: PTM. Package thermal management is supported if set.

Bit 07: HWP. HWP base registers (IA32_PM_ENABLE[bit 0], IA32_HWP_CAPABILITIES,

IA32_HWP_REQUEST, IA32_HWP_STATUS) are supported if set.

Bit 08: HWP_Notification. IA32_HWP_INTERRUPT MSR is supported if set.

Bit 09: HWP_Activity_Window. IA32_HWP_REQUEST[bits 41:32] is supported if set.

Bit 10: HWP_Energy_Performance_Preference. IA32_HWP_REQUEST[bits 31:24] is supported if set.

Bit 11: HWP_Package_Level_Request. IA32_HWP_REQUEST_PKG MSR is supported if set.

Bit 12: Reserved.

Bit 13: HDC. HDC base registers IA32_PKG_HDC_CTL, IA32_PM_CTL1, IA32_THREAD_STALL MSRs are

supported if set.

Bits 31 - 15: Reserved.

EBX

Bits 03 - 00: Number of Interrupt Thresholds in Digital Thermal Sensor.

Bits 31 - 04: Reserved.

ECX

Bit 00: Hardware Coordination Feedback Capability (Presence of IA32_MPERF and IA32_APERF). The

capability to provide a measure of delivered processor performance (since last reset of the counters), as

a percentage of the expected processor performance when running at the TSC frequency.

Bits 02 - 01: Reserved = 0.

Bit 03: The processor supports performance-energy bias preference if CPUID.06H:ECX.SETBH[bit 3] is set

and it also implies the presence of a new architectural MSR called IA32_ENERGY_PERF_BIAS (1B0H).

Bits 31 - 04: Reserved = 0.

EDX

Reserved = 0.

Table 3-8. Information Returned by CPUID Instruction (Contd.)

Initial EAX

Value

Information Provided about the Processor