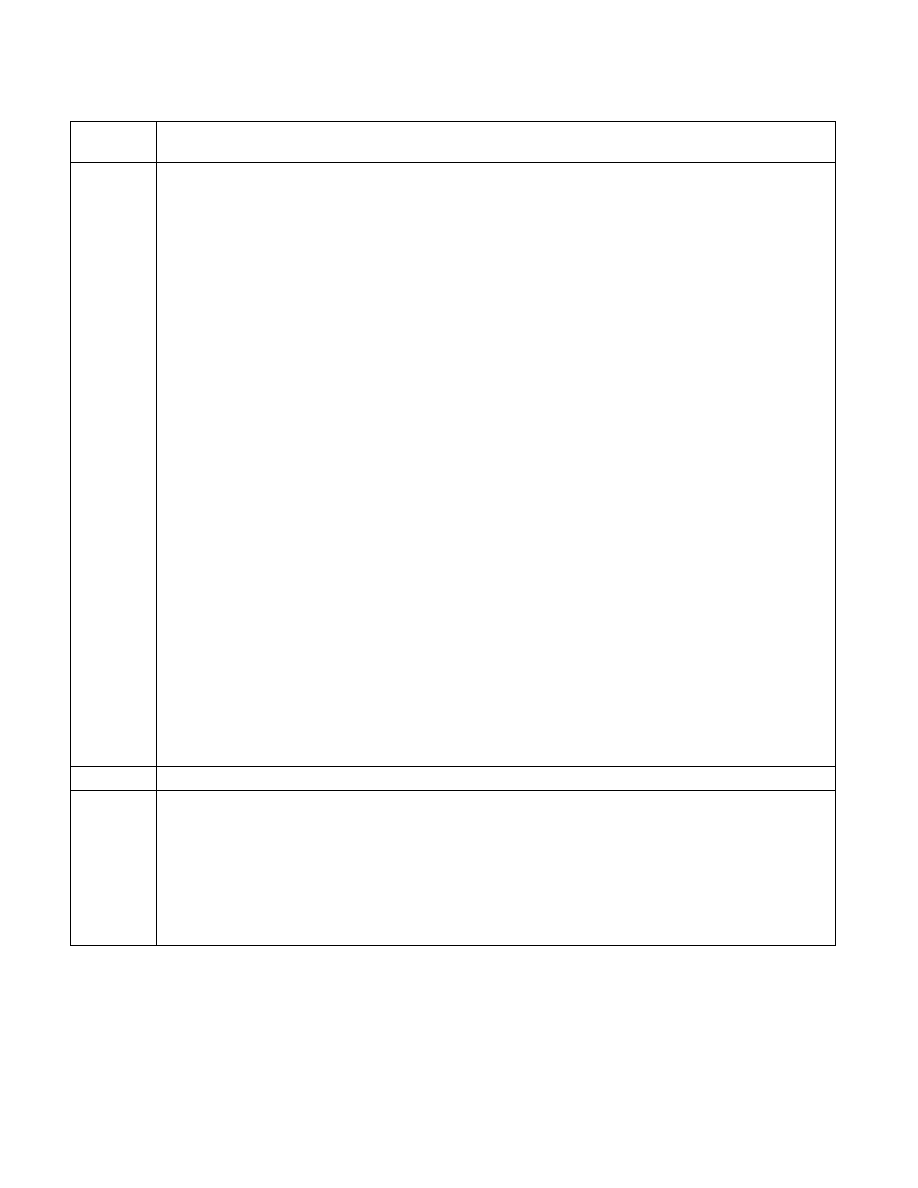

CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

Vol. 2A 3-191

Bits 07 - 05: Cache Level (starts at 1).

Bit 08: Self Initializing cache level (does not need SW initialization).

Bit 09: Fully Associative cache.

Bits 13 - 10: Reserved.

Bits 25 - 14: Maximum number of addressable IDs for logical processors sharing this cache**, ***.

Bits 31 - 26: Maximum number of addressable IDs for processor cores in the physical

package**, ****, *****.

EBX

Bits 11 - 00: L = System Coherency Line Size**.

Bits 21 - 12: P = Physical Line partitions**.

Bits 31 - 22: W = Ways of associativity**.

ECX

Bits 31-00: S = Number of Sets**.

EDX

Bit 00: Write-Back Invalidate/Invalidate.

0 = WBINVD/INVD from threads sharing this cache acts upon lower level caches for threads sharing this

cache.

1 = WBINVD/INVD is not guaranteed to act upon lower level caches of non-originating threads sharing

this cache.

Bit 01: Cache Inclusiveness.

0 = Cache is not inclusive of lower cache levels.

1 = Cache is inclusive of lower cache levels.

Bit 02: Complex Cache Indexing.

0 = Direct mapped cache.

1 = A complex function is used to index the cache, potentially using all address bits.

Bits 31 - 03: Reserved = 0.

NOTES:

* If ECX contains an invalid sub leaf index, EAX/EBX/ECX/EDX return 0. Sub-leaf index n+1 is invalid if sub-

leaf n returns EAX[4:0] as 0.

** Add one to the return value to get the result.

***The nearest power-of-2 integer that is not smaller than (1 + EAX[25:14]) is the number of unique ini-

tial APIC IDs reserved for addressing different logical processors sharing this cache.

**** The nearest power-of-2 integer that is not smaller than (1 + EAX[31:26]) is the number of unique

Core_IDs reserved for addressing different processor cores in a physical package. Core ID is a subset of

bits of the initial APIC ID.

***** The returned value is constant for valid initial values in ECX. Valid ECX values start from 0.

MONITOR/MWAIT Leaf

05H

EAX

Bits 15 - 00: Smallest monitor-line size in bytes (default is processor's monitor granularity).

Bits 31 - 16: Reserved = 0.

EBX

Bits 15 - 00: Largest monitor-line size in bytes (default is processor's monitor granularity).

Bits 31 - 16: Reserved = 0.

ECX

Bit 00: Enumeration of Monitor-Mwait extensions (beyond EAX and EBX registers) supported.

Bit 01: Supports treating interrupts as break-event for MWAIT, even when interrupts disabled.

Bits 31 - 02: Reserved.

Table 3-8. Information Returned by CPUID Instruction (Contd.)

Initial EAX

Value

Information Provided about the Processor