SAFER MODE EXTENSIONS REFERENCE

6-2 Vol. 2D

•

Bit 0 is a lock bit. If the lock bit is clear, an attempt to execute VMXON will cause a general-protection exception.

Attempting to execute GETSEC[SENTER] when the lock bit is clear will also cause a general-protection

exception. If the lock bit is set, WRMSR to the IA32_FEATURE_CONTROL MSR will cause a general-protection

exception. Once the lock bit is set, the MSR cannot be modified until a power-on reset. System BIOS can use

this bit to provide a setup option for BIOS to disable support for VMX, SMX or both VMX and SMX.

•

Bit 1 enables VMX in SMX operation (between executing the SENTER and SEXIT leaves of GETSEC). If this bit is

clear, an attempt to execute VMXON in SMX will cause a general-protection exception if executed in SMX

operation. Attempts to set this bit on logical processors that do not support both VMX operation (Chapter 6,

“Safer Mode Extensions Reference”) and SMX operation cause general-protection exceptions.

•

Bit 2 enables VMX outside SMX operation. If this bit is clear, an attempt to execute VMXON will cause a general-

protection exception if executed outside SMX operation. Attempts to set this bit on logical processors that do

not support VMX operation cause general-protection exceptions.

•

Bits 8 through 14 specify enabled functionality of the SENTER leaf function. Each bit in the field represents an

enable control for a corresponding SENTER function. Only enabled SENTER leaf functionality can be used when

executing SENTER.

•

Bits 15 specify global enable of all SENTER functionalities.

6.2.2

SMX Instruction Summary

System software must first query for available GETSEC leaf functions by executing GETSEC[CAPABILITIES]. The

CAPABILITIES leaf function returns a bit map of available GETSEC leaves. An attempt to execute an unsupported

leaf index results in an undefined opcode (#UD) exception.

6.2.2.1

GETSEC[CAPABILITIES]

The SMX functionality provides an architectural interface for newer processor generations to extend SMX capabili-

ties. Specifically, the GETSEC instruction provides a capability leaf function for system software to discover the

available GETSEC leaf functions that are supported in a processor. Table 6-2 lists the currently available GETSEC

leaf functions.

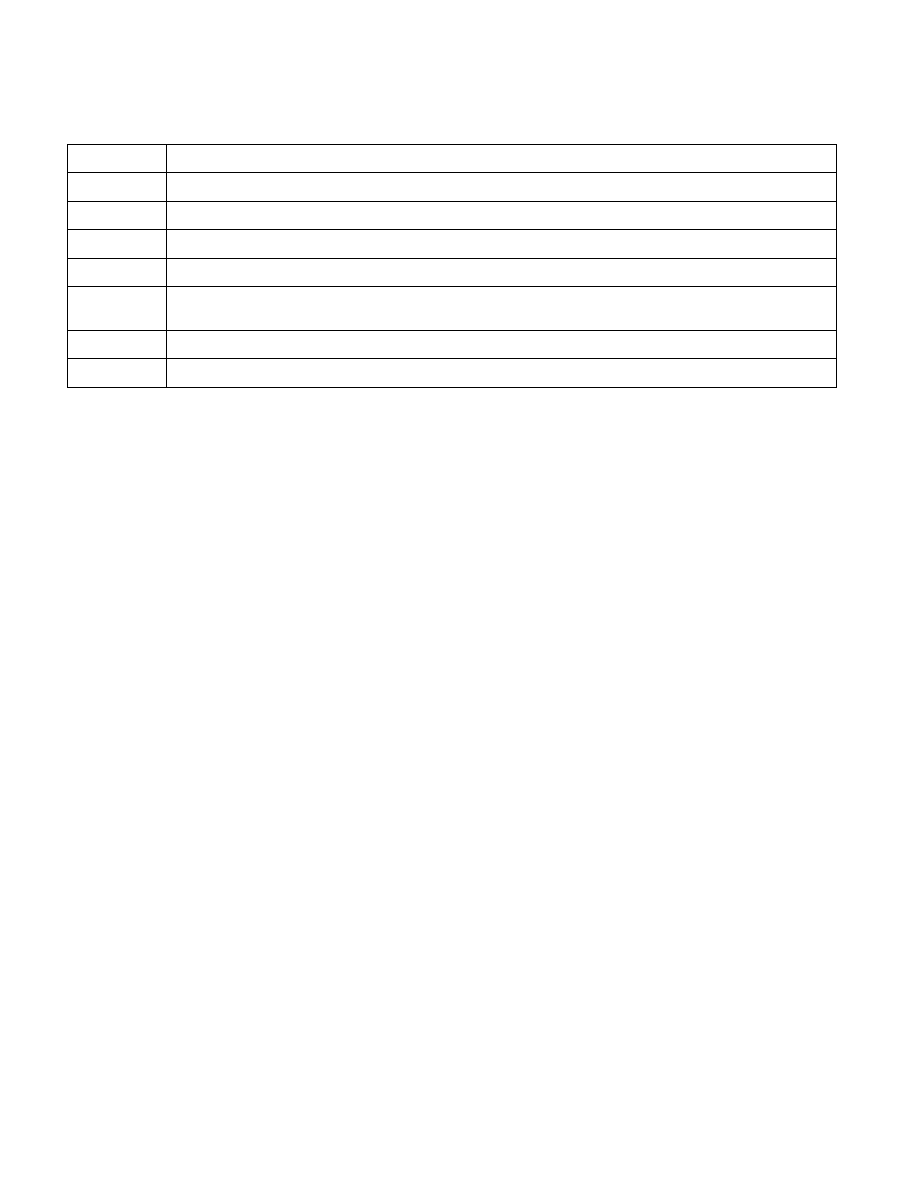

Table 6-1. Layout of IA32_FEATURE_CONTROL

Bit Position

Description

0

Lock bit (0 = unlocked, 1 = locked). When set to '1' further writes to this MSR are blocked.

1

Enable VMX in SMX operation.

2

Enable VMX outside SMX operation.

7:3

Reserved

14:8

SENTER Local Function Enables: When set, each bit in the field represents an enable control for a corresponding

SENTER function.

15

SENTER Global Enable: Must be set to ‘1’ to enable operation of GETSEC[SENTER].

63:16

Reserved