PSHUFB — Packed Shuffle Bytes

INSTRUCTION SET REFERENCE, M-U

4-414 Vol. 2B

index[3..0] SRC2[128 + (i*8)+3 .. (i*8)+0];

DEST[128 + (i*8)+7..(i*8)+0] SRC1[128 + (index*8+7)..(index*8+0)];

endif

}

VPSHUFB (EVEX encoded versions)

(KL, VL) = (16, 128), (32, 256), (64, 512)

jmask (KL-1) & ~0xF

// 0x00, 0x10, 0x30 depending on the VL

FOR j = 0 TO KL-1

// dest

IF kl[ i ] or no_masking

index src.byte[ j ];

IF index & 0x80

Dest.byte[ j ] 0;

ELSE

index (index & 0xF) + (j & jmask);

// 16-element in-lane lookup

Dest.byte[ j ] src.byte[ index ];

ELSE if zeroing

Dest.byte[ j ] 0;

DEST[MAX_VL-1:VL] 0;

Intel C/C++ Compiler Intrinsic Equivalent

VPSHUFB __m512i _mm512_shuffle_epi8(__m512i a, __m512i b);

VPSHUFB __m512i _mm512_mask_shuffle_epi8(__m512i s, __mmask64 k, __m512i a, __m512i b);

VPSHUFB __m512i _mm512_maskz_shuffle_epi8( __mmask64 k, __m512i a, __m512i b);

VPSHUFB __m256i _mm256_mask_shuffle_epi8(__m256i s, __mmask32 k, __m256i a, __m256i b);

VPSHUFB __m256i _mm256_maskz_shuffle_epi8( __mmask32 k, __m256i a, __m256i b);

VPSHUFB __m128i _mm_mask_shuffle_epi8(__m128i s, __mmask16 k, __m128i a, __m128i b);

VPSHUFB __m128i _mm_maskz_shuffle_epi8( __mmask16 k, __m128i a, __m128i b);

PSHUFB: __m64 _mm_shuffle_pi8 (__m64 a, __m64 b)

(V)PSHUFB: __m128i _mm_shuffle_epi8 (__m128i a, __m128i b)

VPSHUFB:__m256i _mm256_shuffle_epi8(__m256i a, __m256i b)

SIMD Floating-Point Exceptions

None.

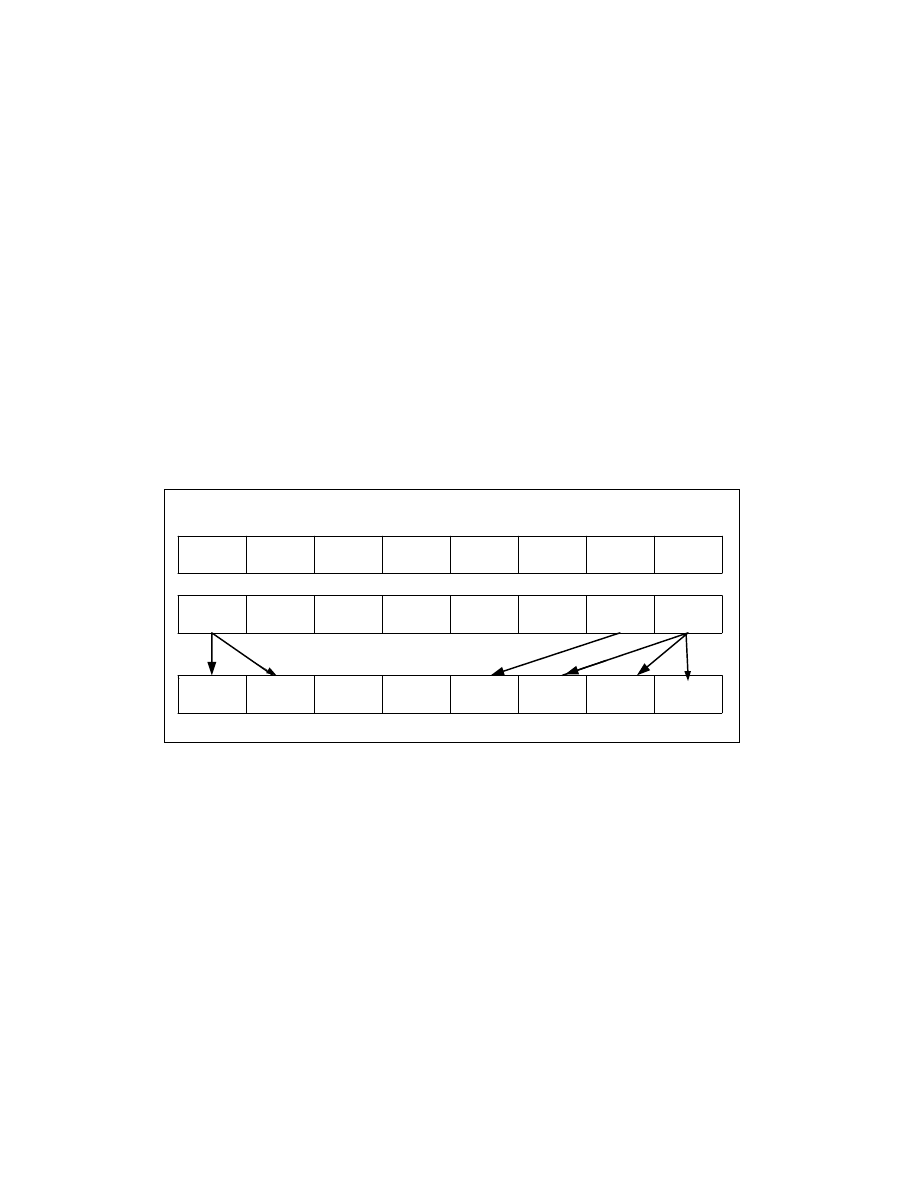

Figure 4-15. PSHUFB with 64-Bit Operands

07H 07H FFH 80H 01H 00H 00H 00H

04H 01H 07H 03H 02H 02H FFH 01H

04H 04H 00H 00H FFH 01H 01H 01H

MM2

MM1

MM1