E-8 Vol. 1

GUIDELINES FOR WRITING SIMD FLOATING-POINT EXCEPTION HANDLERS

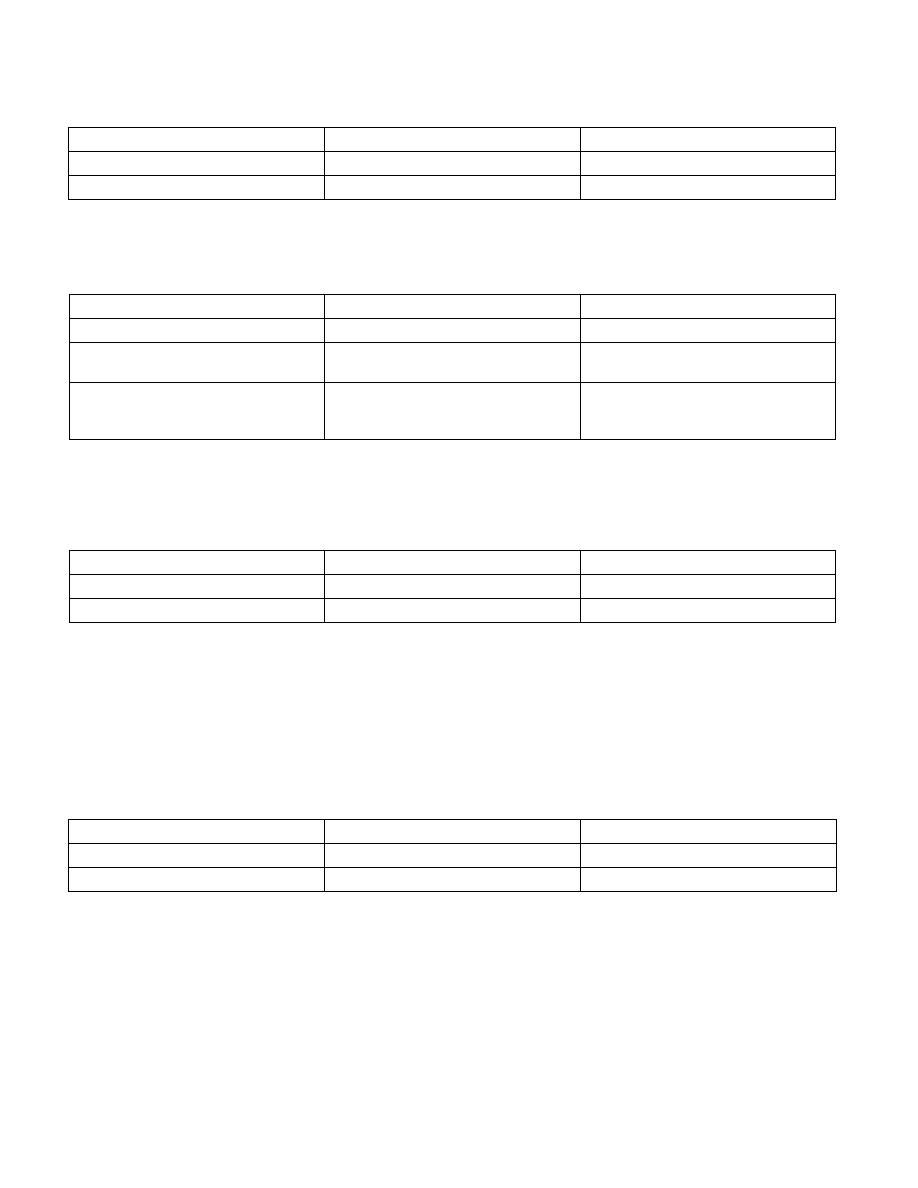

Table E-9. MAXPS, MAXSS, MINPS, MINSS, MAXPD, MAXSD, MINPD, MINSD

Source Operands

Masked Result

Unmasked Result

Opd1 op NaN2 (any Opd1)

NaN2

None

NaN1 op Opd2 (any Opd2)

Opd2

None

NOTE:

1. SNaN and QNaN operands raise an Invalid Operation fault.

Table E-10. SQRTPS, SQRTSS, SQRTPD, SQRTSD

Source Operand

Masked Result

Unmasked Result

QNaN

QNaN

QNaN (not an exception)

SNaN

SNaN | 00400000H or

SNaN | 0008000000000000H

1

None

Source operand is not SNaN;

but #I is signaled (e.g. for

sqrt (-1.0))

Single precision or

double precision QNaN Indefinite

None

NOTE:

1. SNaN | 00400000H is a quiet NaN in single precision format (if SNaN is in single precision) and SNaN | 0008000000000000H is a

quiet NaN in double precision format (if SNaN is in double precision), obtained from the signaling NaN given as input.

Table E-11. CVTPS2PD, CVTSS2SD

Source Operands

Masked Result

Unmasked Result

QNaN

QNaN1

1

QNaN1

1

(not an exception)

SNaN

QNaN1

2

None

NOTES:

1. The double precision output QNaN1 is created from the single precision input QNaN as follows: the sign bit is preserved, the 8-bit

exponent FFH is replaced by the 11-bit exponent 7FFH, and the 24-bit significand is extended to a 53-bit significand by appending

29 bits equal to 0.

2. The double precision output QNaN1 is created from the single precision input SNaN as follows: the sign bit is preserved, the 8-bit

exponent FFH is replaced by the 11-bit exponent 7FFH, and the 24-bit significand is extended to a 53-bit significand by pending

29 bits equal to 0. The second most significant bit of the significand is changed from 0 to 1 to convert the signaling NaN into a

quiet NaN.

Table E-12. CVTPD2PS, CVTSD2SS

Source Operands

Masked Result

Unmasked Result

QNaN

QNaN1

1

QNaN1

1

(not an exception)

SNaN

QNaN1

2

None

NOTES:

1. The single precision output QNaN1 is created from the double precision input QNaN as follows: the sign bit is preserved, the 11-bit

exponent 7FFH is replaced by the 8-bit exponent FFH, and the 53-bit significand is truncated to a 24-bit significand by removing its

29 least significant bits.

2. The single precision output QNaN1 is created from the double precision input SNaN as follows: the sign bit is preserved, the 11-bit

exponent 7FFH is replaced by the 8-bit exponent FFH, and the 53-bit significand is truncated to a 24-bit significand by removing its

29 least significant bits. The second most significant bit of the significand is changed from 0 to 1 to convert the signaling NaN into

a quiet NaN.