Vol. 1 E-7

GUIDELINES FOR WRITING SIMD FLOATING-POINT EXCEPTION HANDLERS

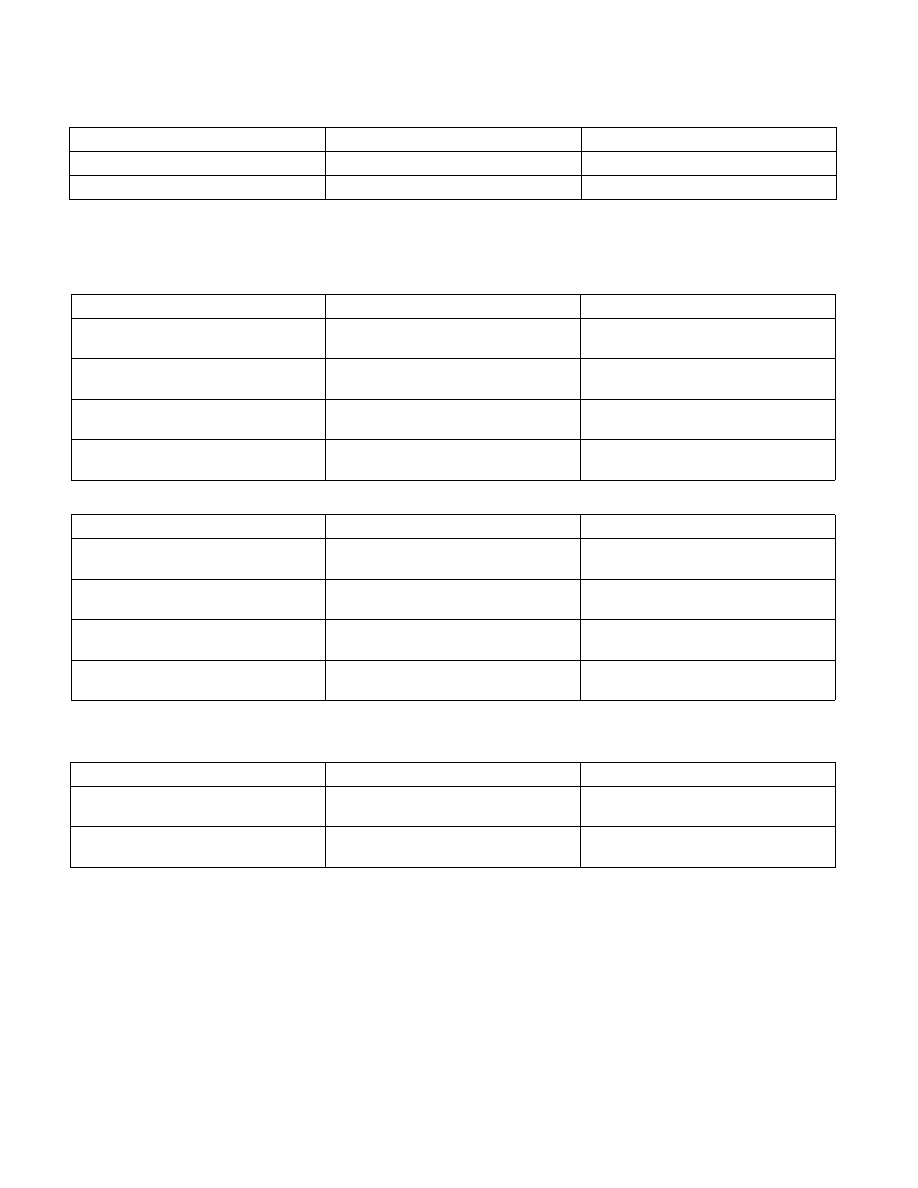

Table E-5. CMPPS.NLT, CMPSS.NLT, CMPPS.NLE, CMPSS.NLE, CMPPD.NLT, CMPSD.NLT, CMPPD.NLE, CMPSD.NLE

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

FFFFFFFFH or FFFFFFFFFFFFFFFFH

1

None

Opd1 op NaN (any Opd1)

FFFFFFFFH or FFFFFFFFFFFFFFFFH

1

None

NOTE:

1. 32-bit results are for single, and 64-bit results for double precision operations.

Table E-6. COMISS, COMISD

Source Operands

Masked Result

Unmasked Result

SNaN op Opd2 (any Opd2)

OF, SF, AF = 000

ZF, PF, CF = 111

None

Opd1 op SNaN (any Opd1)

OF, SF, AF = 000

ZF, PF, CF = 111

None

QNaN op Opd2 (any Opd2)

OF, SF, AF = 000

ZF, PF, CF = 111

None

Opd1 op QNaN (any Opd1)

OF, SF, AF = 000

ZF, PF, CF = 111

None

Table E-7. UCOMISS, UCOMISD

Source Operands

Masked Result

Unmasked Result

SNaN op Opd2 (any Opd2)

OF, SF, AF = 000

ZF, PF, CF = 111

None

Opd1 op SNaN (any Opd1)

OF, SF, AF = 000

ZF, PF, CF = 111

None

QNaN op Opd2

(any Opd2

≠

SNaN)

OF, SF, AF = 000

ZF, PF, CF = 111

OF, SF, AF = 000

ZF, PF, CF = 111 (not an exception)

Opd1 op QNaN

(any Opd1

≠

SNaN)

OF, SF, AF = 000

ZF, PF, CF = 111

OF, SF, AF = 000

ZF, PF, CF = 111 (not an exception)

Table E-8. CVTPS2PI, CVTSS2SI, CVTTPS2PI, CVTTSS2SI, CVTPD2PI, CVTSD2SI, CVTTPD2PI, CVTTSD2SI,

CVTPS2DQ, CVTTPS2DQ, CVTPD2DQ, CVTTPD2DQ

Source Operand

Masked Result

Unmasked Result

SNaN

80000000H or 8000000000000000

1

(Integer Indefinite)

None

QNaN

80000000H or 8000000000000000

1

(Integer Indefinite)

None

NOTE:

1. 32-bit results are for single, and 64-bit results for double precision operations.