E-6 Vol. 1

GUIDELINES FOR WRITING SIMD FLOATING-POINT EXCEPTION HANDLERS

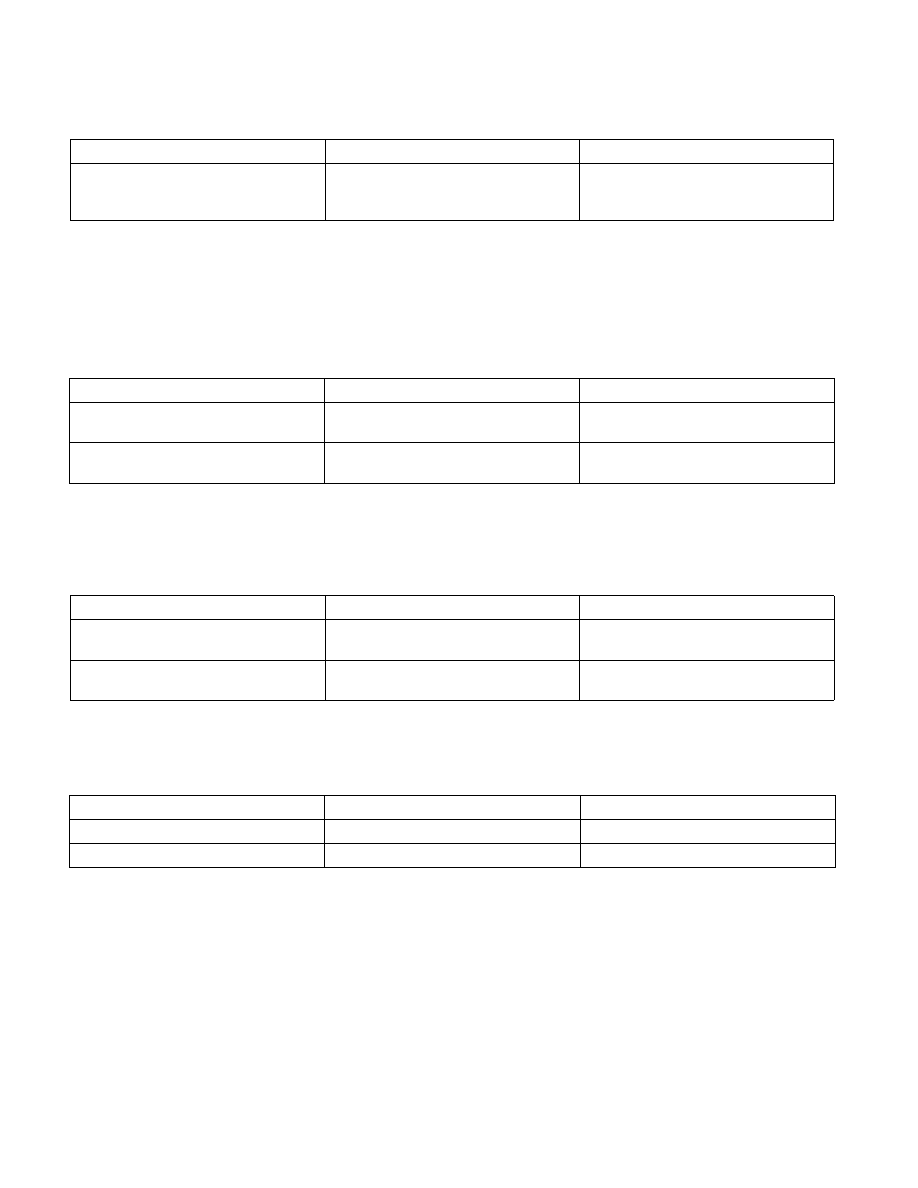

Neither source operand is SNaN,

but #I is signaled (e.g. for Inf - Inf,

Inf ∗ 0, Inf / Inf, 0/0)

Single precision or double precision QNaN

Indefinite

None

NOTES:

1. For Tables E-1 to E-12: op denotes the operation to be performed.

2. SNaN | 00400000H is a quiet NaN in single precision format (if SNaN is in single precision) and SNaN | 0008000000000000H is a

quiet NaN in double precision format (if SNaN is in double precision), obtained from the signaling NaN given as input.

3. Operations involving only quiet NaNs do not raise floating-point exceptions.

Table E-2. CMPPS.EQ, CMPSS.EQ, CMPPS.ORD, CMPSS.ORD,

CMPPD.EQ, CMPSD.EQ, CMPPD.ORD, CMPSD.ORD

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

00000000H or 0000000000000000H

1

00000000H or 0000000000000000H

1

(not an exception)

Opd1 op NaN (any Opd1)

00000000H or 0000000000000000H

1

00000000H or 0000000000000000H

1

(not an exception)

NOTE:

1. 32-bit results are for single, and 64-bit results for double precision operations.

Table E-3. CMPPS.NEQ, CMPSS.NEQ, CMPPS.UNORD, CMPSS.UNORD, CMPPD.NEQ, CMPSD.NEQ,

CMPPD.UNORD, CMPSD.UNORD

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

FFFFFFFFH or FFFFFFFFFFFFFFFFH

1

FFFFFFFFH or FFFFFFFFFFFFFFFFH

1

(not

an exception)

Opd1 op NaN (any Opd1)

FFFFFFFFH or FFFFFFFFFFFFFFFFH

1

FFFFFFFFH or FFFFFFFFFFFFFFFFH

1

(not

an exception)

NOTE:

1. 32-bit results are for single, and 64-bit results for double precision operations.

Table E-4. CMPPS.LT, CMPSS.LT, CMPPS.LE, CMPSS.LE, CMPPD.LT, CMPSD.LT, CMPPD.LE, CMPSD.LE

Source Operands

Masked Result

Unmasked Result

NaN op Opd2 (any Opd2)

00000000H or 0000000000000000H

1

None

Opd1 op NaN (any Opd1)

00000000H or 0000000000000000H

1

None

NOTE:

1. 32-bit results are for single, and 64-bit results for double precision operations.

Table E-1. ADDPS, ADDSS, SUBPS, SUBSS, MULPS, MULSS, DIVPS, DIVSS, ADDPD, ADDSD, SUBPD, SUBSD, MULPD,

MULSD, DIVPD, DIVSD, ADDSUBPS, ADDSUBPD, HADDPS, HADDPD, HSUBPS, HSUBPD (Contd.)

Source Operands

Masked Result

Unmasked Result