Vol. 1 14-35

PROGRAMMING WITH AVX, FMA AND AVX2

14.10 SIMD FLOATING-POINT EXCEPTIONS

AVX instructions can generate SIMD floating-point exceptions (#XM) and respond to exception masks in the same

way as Legacy SSE instructions. When CR4.OSXMMEXCPT=0 any unmasked FP exceptions generate an Undefined

Opcode exception (#UD).

AVX FP exceptions are created in a similar fashion (differing only in number of elements) to Legacy SSE and SSE2

instructions capable of generating SIMD floating-point exceptions.

AVX introduces no new arithmetic operations (AVX floating-point are analogues of existing Legacy SSE instruc-

tions).

F16C, FMA instructions can generate SIMD floating-point exceptions (#XM). The requirement that apply to AVX

also apply to F16C and FMA.

The subset of AVX2 instructions that operate on floating-point data do not generate #XM.

The detailed exception conditions for AVX instructions and legacy SIMD instructions (excluding instructions that

operates on MMX registers) are described in a number of exception class types, depending on the operand syntax

and memory operation characteristics. The complete list of SIMD instruction exception class types are defined in

Chapter 2, “Instruction Format,” of Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A.

14.11 EMULATION

Setting the CR0.EMbit to 1 provides a technique to emulate Legacy SSE floating-point instruction sets in software.

This technique is not supported with AVX instructions.

If an operating system wishes to emulate AVX instructions, set XCR0[2:1] to zero. This will cause AVX instructions

to #UD. Emulation of F16C, AVX2, and FMA by operating system can be done similarly as with emulating AVX

instructions.

14.12 WRITING AVX FLOATING-POINT EXCEPTION HANDLERS

AVX and FMA floating-point exceptions are handled in an entirely analogous way to Legacy SSE floating-point

exceptions. To handle unmasked SIMD floating-point exceptions, the operating system or executive must provide

an exception handler. The section titled “SSE and SSE2 SIMD Floating-Point Exceptions” in Chapter 11, “Program-

ming with Streaming SIMD Extensions 2 (SSE2),” describes the SIMD floating-point exception classes and gives

suggestions for writing an exception handler to handle them.

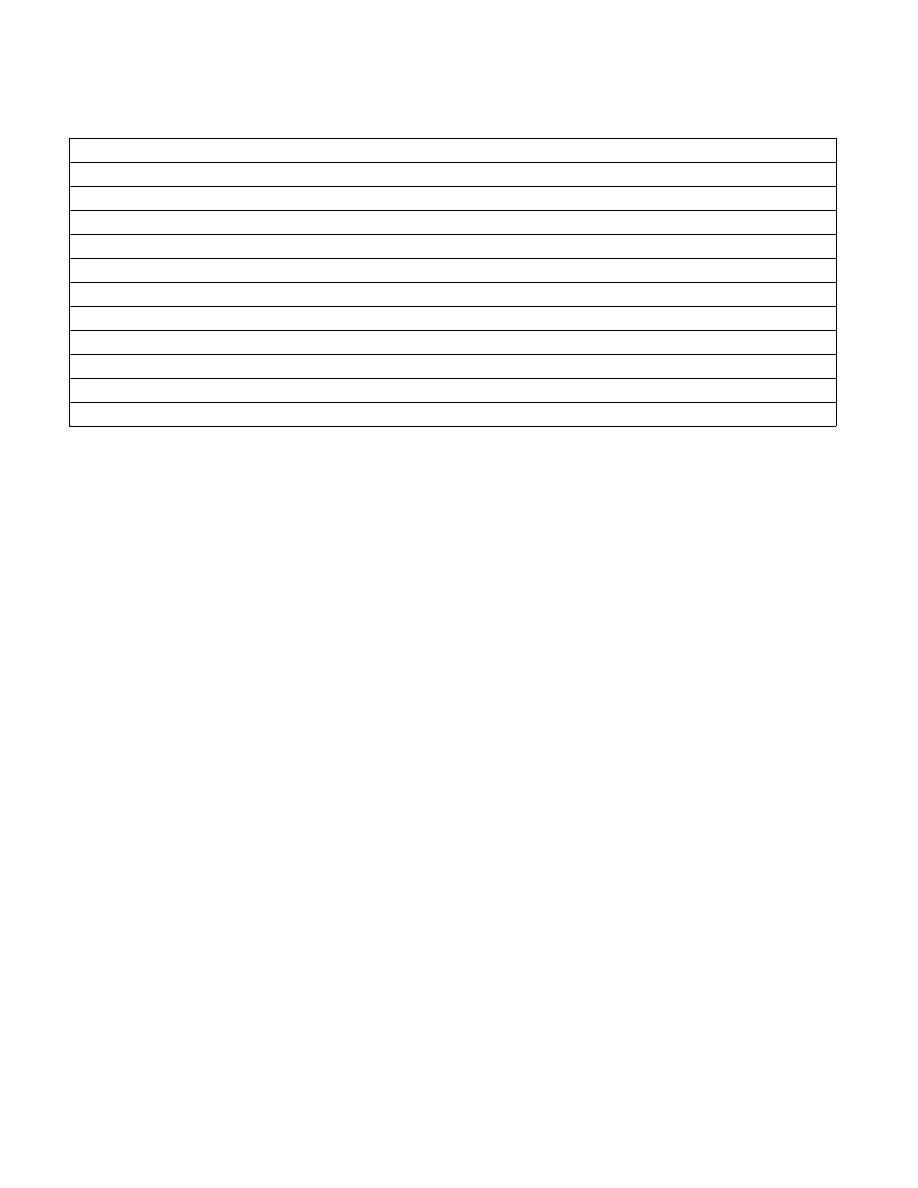

Table 14-23. Instructions Not Requiring Explicit Memory Alignment

(V)MOVDQU xmm, m128

(V)MOVDQU m128, m128

(V)MOVUPS xmm, m128

(V)MOVUPS m128, xmm

(V)MOVUPD xmm, m128

(V)MOVUPD m128, xmm

VMOVDQU ymm, m256

VMOVDQU m256, ymm

VMOVUPS ymm, m256

VMOVUPS m256, ymm

VMOVUPD ymm, m256

VMOVUPD m256, ymm